## TPU 2735

## Contents

| Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Section                                                                                                                                                                                                                                                          | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.                                                                                                                                                                                                                                                               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.                                                                                                                                                                                                                                                               | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.                                                                                                                                                                                                                                                               | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.1.                                                                                                                                                                                                                                                             | Outline Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.2.                                                                                                                                                                                                                                                             | Pin Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.2.1.                                                                                                                                                                                                                                                           | 40-Pin DIL Plastic Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.2.2.                                                                                                                                                                                                                                                           | 44-Pin PLCC Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.3.                                                                                                                                                                                                                                                             | Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

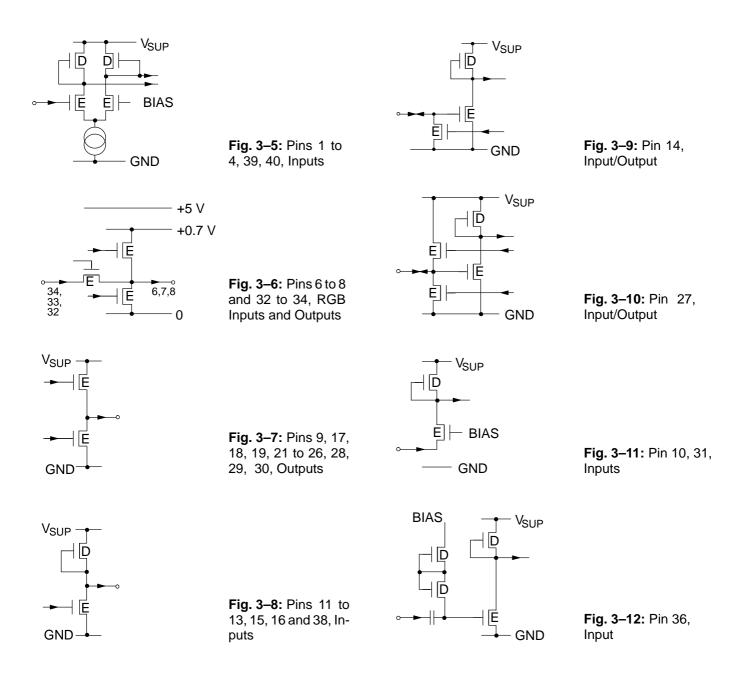

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.4.                                                                                                                                                                                                                                                             | Pin Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.5.                                                                                                                                                                                                                                                             | Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.5.1.                                                                                                                                                                                                                                                           | Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.5.2.                                                                                                                                                                                                                                                           | Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.5.3.                                                                                                                                                                                                                                                           | Characteristics of the Digital Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.5.4.                                                                                                                                                                                                                                                           | Characteristics, RGB Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.5.5.                                                                                                                                                                                                                                                           | Characteristics of the External RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.                                                                                                                                                                                                                                                               | Various Operation Modes of the TPU 2735                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.1.                                                                                                                                                                                                                                                             | The Menu Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2.                                                                                                                                                                                                                                                             | Teletext Display without Interlaced Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.3.                                                                                                                                                                                                                                                             | The Effect of Errors in the Transmission of Teletext Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.3.1.                                                                                                                                                                                                                                                           | Errors in the Hamming-Code Protected Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.3.2.                                                                                                                                                                                                                                                           | Errors in Data with Parity Check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.4.                                                                                                                                                                                                                                                             | Multipage Conflict Situation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.                                                                                                                                                                                                                                                               | RAM Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 16<br>17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.<br>6.                                                                                                                                                                                                                                                         | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6.                                                                                                                                                                                                                                                               | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>17</b><br>17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>6.</b><br>6.1.                                                                                                                                                                                                                                                | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>17</b><br>17<br>18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>6.</b><br>6.1.<br>6.2.                                                                                                                                                                                                                                        | <b>Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070</b><br>The Address Commands<br>The Data Transfer Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 17<br>17<br>18<br>18<br>18<br>18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> </ol>                                                                                                                                                                                               | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands<br>The Data Transfer Command<br>The Status Test Command<br>The IM Bus Hardware Test/Configuration Register<br>The Control Registers of Register Chain 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>17</b><br>17<br>18<br>18<br>18<br><b>19</b><br>19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>7.1.</li> </ol>                                                                                                                                                                                 | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands<br>The Data Transfer Command<br>The Status Test Command<br>The IM Bus Hardware Test/Configuration Register<br>The Control Registers of Register Chain 2<br>The Page Request Registers, R-PRx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <ol> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>20</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>7.</li> <li>7.1.</li> <li>7.2.</li> </ol>                                                                                                                                                       | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands<br>The Data Transfer Command<br>The Status Test Command<br>The IM Bus Hardware Test/Configuration Register<br>The Control Registers of Register Chain 2<br>The Page Request Registers, R-PRx<br>The Page Selection Register, R-PS                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ol> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>20</li> <li>20</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> </ol>                                                                                                                                         | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands<br>The Data Transfer Command<br>The Status Test Command<br>The IM Bus Hardware Test/Configuration Register<br>The Control Registers of Register Chain 2<br>The Page Request Registers, R-PRx<br>The Page Selection Register, R-PS<br>The Subcode Register, R-SC                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ol> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>20</li> <li>20</li> <li>21</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> <li>7.4.</li> </ol>                                                                                                                                       | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands<br>The Data Transfer Command<br>The Status Test Command<br>The IM Bus Hardware Test/Configuration Register<br>The Control Registers of Register Chain 2<br>The Page Request Registers, R-PRx<br>The Page Selection Register, R-PS<br>The Subcode Register, R-SC<br>The Display Selection Register, R-DS                                                                                                                                                                                                                                                                                                                                                                            |

| <ol> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>20</li> <li>20</li> <li>21</li> <li>21</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> <li>7.4.</li> <li>7.5.</li> </ol>                                                                                                             | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands<br>The Data Transfer Command<br>The Status Test Command<br>The IM Bus Hardware Test/Configuration Register<br>The IM Bus Hardware Test/Configuration Register<br>The Page Request Registers of Register Chain 2<br>The Page Request Registers, R-PRx<br>The Page Request Register, R-PS<br>The Subcode Register, R-SC<br>The Display Selection Register, R-DS<br>The Data Acquisition Control Register, R-DAC                                                                                                                                                                                                                                                                      |

| <ol> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>20</li> <li>20</li> <li>21</li> <li>21</li> <li>22</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> <li>7.4.</li> <li>7.5.</li> <li>7.6.</li> </ol>                                                                                               | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands<br>The Data Transfer Command<br>The Status Test Command<br>The IM Bus Hardware Test/Configuration Register<br>The Control Registers of Register Chain 2<br>The Page Request Registers, R-PRx<br>The Page Selection Register, R-PS<br>The Subcode Register, R-SC<br>The Display Selection Register, R-DS<br>The Data Acquisition Control Register, R-DAC<br>The Status Indicator Register, R-SI                                                                                                                                                                                                                                                                                     |

| <ol> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>20</li> <li>20</li> <li>21</li> <li>21</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> <li>7.4.</li> <li>7.5.</li> </ol>                                                                                                             | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands<br>The Data Transfer Command<br>The Status Test Command<br>The IM Bus Hardware Test/Configuration Register<br>The Control Registers of Register Chain 2<br>The Page Request Registers, R-PRx<br>The Page Selection Register, R-PS<br>The Subcode Register, R-SC<br>The Display Selection Register, R-DS<br>The Data Acquisition Control Register, R-DAC<br>The Status Indicator Register, R-SI<br>The Display Control Registers, R-DC1 to R-DC6                                                                                                                                                                                                                                    |

| <ol> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>20</li> <li>20</li> <li>21</li> <li>21</li> <li>22</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> <li>7.4.</li> <li>7.5.</li> <li>7.6.</li> </ol>                                                                                               | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands<br>The Data Transfer Command<br>The Status Test Command<br>The IM Bus Hardware Test/Configuration Register<br>The Control Registers of Register Chain 2<br>The Page Request Registers, R-PRx<br>The Page Selection Register, R-PS<br>The Subcode Register, R-SC<br>The Display Selection Register, R-DS<br>The Data Acquisition Control Register, R-DAC<br>The Status Indicator Register, R-SI                                                                                                                                                                                                                                                                                     |

| <ol> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>20</li> <li>20</li> <li>21</li> <li>21</li> <li>22</li> <li>23</li> <li>27</li> <li>28</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ol> <li>6.</li> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> <li>7.4.</li> <li>7.5.</li> <li>7.6.</li> <li>7.7.</li> <li>7.8.</li> <li>8.</li> </ol>                                           | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands<br>The Data Transfer Command<br>The Data Transfer Command<br>The Status Test Command<br>The IM Bus Hardware Test/Configuration Register<br>The Control Registers of Register Chain 2<br>The Page Request Registers, R-PRx<br>The Page Request Register, R-PS<br>The Subcode Register, R-SC<br>The Display Selection Register, R-DS<br>The Data Acquisition Control Register, R-DAC<br>The Status Indicator Register, R-SI<br>The Display Control Registers, R-DC1 to R-DC6<br>The Memory Control Register, R-MC<br>The Control Registers of Register Chain 1                                                                                                                       |

| <ol> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>20</li> <li>20</li> <li>21</li> <li>21</li> <li>22</li> <li>23</li> <li>27</li> <li>28</li> <li>28</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                         | <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> <li>7.4.</li> <li>7.5.</li> <li>7.6.</li> <li>7.7.</li> <li>7.8.</li> <li>8.</li> <li>8.1.</li> </ol>                                         | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands<br>The Data Transfer Command<br>The Data Transfer Command<br>The Status Test Command<br>The IM Bus Hardware Test/Configuration Register<br>The Control Registers of Register Chain 2<br>The Page Request Registers, R-PRx<br>The Page Selection Register, R-PS<br>The Subcode Register, R-SC<br>The Display Selection Register, R-DS<br>The Data Acquisition Control Register, R-DAC<br>The Status Indicator Register, R-SI<br>The Display Control Registers, R-DC1 to R-DC6<br>The Memory Control Register, R-MC<br>The Page Identification Register, R-PI                                                                                                                        |

| <ol> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>20</li> <li>20</li> <li>21</li> <li>21</li> <li>22</li> <li>23</li> <li>27</li> <li>28</li> <li>28</li> <li>28</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                             | <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> <li>7.4.</li> <li>7.5.</li> <li>7.6.</li> <li>7.7.</li> <li>7.8.</li> <li>8.1.</li> <li>8.2.</li> </ol>                                       | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands<br>The Data Transfer Command<br>The Data Transfer Command<br>The Status Test Command<br>The IM Bus Hardware Test/Configuration Register<br>The Control Registers of Register Chain 2<br>The Page Request Registers, R-PRx<br>The Page Request Register, R-PS<br>The Subcode Register, R-SC<br>The Display Selection Register, R-DS<br>The Data Acquisition Control Register, R-DAC<br>The Status Indicator Register, R-SI<br>The Display Control Registers, R-DC1 to R-DC6<br>The Memory Control Register, R-MC<br>The Page Identification Register, R-PI<br>The Page Identification Register, R-PI<br>The Control Bit Register 1, R-CB1                                           |

| <ol> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>20</li> <li>20</li> <li>21</li> <li>21</li> <li>22</li> <li>23</li> <li>27</li> <li>28</li> <li>28</li> <li>28</li> <li>28</li> <li>28</li> <li>28</li> <li>28</li> <li>28</li> </ol>                                                                                                                                                                                                                                                                                                                                                 | <ol> <li>6.</li> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> <li>7.4.</li> <li>7.5.</li> <li>7.6.</li> <li>7.7.</li> <li>7.8.</li> <li>8.</li> <li>8.1.</li> <li>8.2.</li> <li>8.3.</li> </ol> | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands<br>The Data Transfer Command<br>The Status Test Command<br>The IM Bus Hardware Test/Configuration Register<br>The Control Registers of Register Chain 2<br>The Page Request Registers, R-PRx<br>The Page Request Register, R-PS<br>The Subcode Register, R-SC<br>The Display Selection Register, R-DS<br>The Data Acquisition Control Register, R-DAC<br>The Status Indicator Register, R-SI<br>The Display Control Registers, R-DC1 to R-DC6<br>The Memory Control Register, R-MC<br>The Page Identification Register, R-PI<br>The Page Identification Register, R-PI<br>The Control Bit Register 1, R-CB1<br>The Control Bit Register 2, R-CB2                                   |

| <ol> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>20</li> <li>20</li> <li>21</li> <li>21</li> <li>22</li> <li>23</li> <li>27</li> <li>28</li> </ol> | <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> <li>7.4.</li> <li>7.5.</li> <li>7.6.</li> <li>7.7.</li> <li>7.8.</li> <li>8.1.</li> <li>8.2.</li> <li>8.3.</li> <li>8.4.</li> </ol>           | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands<br>The Data Transfer Command<br>The Data Transfer Command<br>The Status Test Command<br>The IM Bus Hardware Test/Configuration Register<br>The Control Registers of Register Chain 2<br>The Page Request Registers, R-PRx<br>The Page Request Registers, R-PS<br>The Subcode Register, R-SC<br>The Display Selection Register, R-DS<br>The Data Acquisition Control Register, R-DAC<br>The Data Acquisition Control Register, R-DAC<br>The Display Control Registers, R-DC1 to R-DC6<br>The Memory Control Register, R-MC<br>The Page Identification Register, R-PI<br>The Control Bit Register 1, R-CB1<br>The Control Bit Register 2, R-CB2<br>The Control Bit Register 3, R-CB3 |

| <ol> <li>17</li> <li>18</li> <li>18</li> <li>18</li> <li>19</li> <li>20</li> <li>20</li> <li>21</li> <li>21</li> <li>22</li> <li>23</li> <li>27</li> <li>28</li> <li>28</li> <li>28</li> <li>28</li> <li>28</li> <li>28</li> <li>28</li> <li>28</li> </ol>                                                                                                                                                                                                                                                                                                                                                 | <ol> <li>6.</li> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>7.</li> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> <li>7.4.</li> <li>7.5.</li> <li>7.6.</li> <li>7.7.</li> <li>7.8.</li> <li>8.</li> <li>8.1.</li> <li>8.2.</li> <li>8.3.</li> </ol> | Controlling the TPU 2735 with the CCU 2030, CCU 2050 or CCU 2070<br>The Address Commands<br>The Data Transfer Command<br>The Status Test Command<br>The IM Bus Hardware Test/Configuration Register<br>The Control Registers of Register Chain 2<br>The Page Request Registers, R-PRx<br>The Page Request Register, R-PS<br>The Subcode Register, R-SC<br>The Display Selection Register, R-DS<br>The Data Acquisition Control Register, R-DAC<br>The Status Indicator Register, R-SI<br>The Display Control Registers, R-DC1 to R-DC6<br>The Memory Control Register, R-MC<br>The Page Identification Register, R-PI<br>The Page Identification Register, R-PI<br>The Control Bit Register 1, R-CB1<br>The Control Bit Register 2, R-CB2                                   |

## Contents, continued

| Page | Section | Title                                    |

|------|---------|------------------------------------------|

| 29   | 9.      | Two Ways to Select a Page for Display    |

| 29   | 10.     | Reset of the TPU 2735 Teletext Processor |

| 30   | 11.     | Application Notes                        |

| 33   | 12.     | Description of the IM Bus                |

#### **Teletext Processor for Level 1 Teletext**

#### Note:

If not otherwise designated the pin numbers mentioned refer to the 40-pin DIL package.

### 1. Introduction

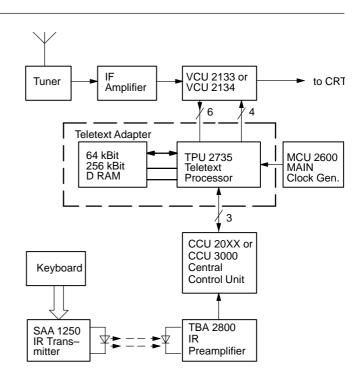

The TPU 2735 is specified to handle Level-1-Teletext information (in Germany: Videotext) as it is transmitted today by the TV broadcast stations in Great Britain, Germany and other European countries. The TPU 2735 is part of the DIGIT 2000 digital TV system and works in conjunction with the other VLSI circuits and processors of this system. This makes the Teletext adapter designed with the TPU 2735 very simple and economic (see Fig. 1–1).

The TPU 2735 is an N-channel VLSI MOS circuit, housed in a 40-pin Dil plastic package and contains on a single silicon chip the following functions:

- one-chip solution of the Teletext processing (except for external RAM)

- ghost compensation to eliminate the effects of ghost pictures due to reflections

- reduced access time is provided for the Teletext pages by receiving and storing up to eight pages in one go

- up to 32 stored pages

- automatic language-dependent character selection

- switchover facility PAL/NTSC/D2MAC

- full level one features (FLOF) support

- level 1.5 Spanish Teletext support

- largely compatible to the TPU 2732/33

Fig. 1–1: Teletext application block diagram

#### 2. Functional Description

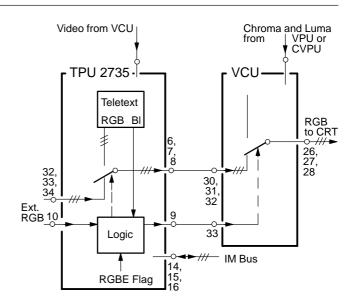

The TPU 2735 whose block diagram is shown in Fig. 2–1, operates according to a rigid timing determined by the vertical cycle of the TV receiver. The data acquisition period starts at line 7 with PAL or line 10 with NTSC and ends at line 22 with PAL or line 21 with NTSC. During this period, the input data is processed by a ghost filter which is able to compensate reflections with short delay time of 0 to 0.8  $\mu$ s for PAL or 0 to 1  $\mu$ s for NTSC. In the D2MAC mode the acquisition is active from line 1 to 22 and line 313 to 334.

In the Data Acquisition Unit the Teletext information is synchronized and identified. A comparator preselects the pages with page numbers that are requested by the CCU 2000 or CCU 3000 Central Control Unit and loads them into the RAM. To eliminate speed problems of the external Dynamic RAM, the data is buffered in an internal RAM buffer (Fig. 2–1). The comparator contained in the data acquisition unit decides into which sector of the DRAM the data is stored.

The display period starts at line 48 with PAL or line 50 with NTSC and ends at line 286 with PAL or line 242 with NTSC. The display control unit selects one of the stored

eight pages for display. The 8-bit character words are transformed into a 6 x 10 dot matrix with PAL or 6 x 8 dot matrix with NTSC by a character generator (ROM) of 96 programmed characters and are displayed in 24 rows of 40 characters each. Optionally, 25 rows can be displayed in PAL/D2MAC. Different character sets are available for eight languages under CCU or transmitter control, the required character set being selected automatically by the control bits C<sub>12</sub> to C<sub>14</sub> of row 0 of the Teletext page displayed. Every tenth line with PAL or every eighth line with NTSC a new Teletext row is loaded from the DRAM into the RAM buffer. When the RAM is not accessed by the TPU 2735, the memory control refreshes the memory and handles CCU requests for RAM access.

Via the IM bus the CCU can access all RAM locations and controls the TPU 2735 by loading the appropriate registers in the RAM, so that the TPU 2735 can be used to display text from other sources. The TPU 2735 can display a list of contents of the stored eight pages (menu) all by itself. The TPU 2735 can use either one 64 Kx1 bit Dynamic RAM or one 256 Kx1 bit Dynamic RAM. So, RAM capacity is flexible to store up to 32 pages. The DRAMs can be standard types (see section 3.).

Fig. 2-1: Block diagram of the TPU 2735

## TPU 2735

## 3. Specifications

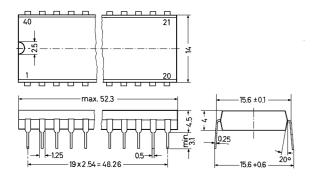

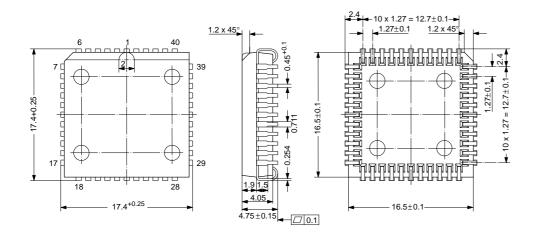

## 3.1. Outline Dimensions

Fig. 3–1: TPU 2735 in 40-pin DIL packageWeight approx. 6 g,Dimensions in mm

Fig. 3–2: TPU 2735 in 44-pin PLCC package, Weight approx. 2.2 g, Dimensions in mm

#### 3.2. Pin Connections

#### 3.2.1. 40-Pin Dil Plastic Package

- 1. V3 Video Input

- 2 V4 Video Input

- 3 V5 Video Input

- 4 V6 Video Input (MSB)

- 5 GND

- 6 R Output

- 7 G Output

- 8 B Output

- 9 Fast Blanking Output

- 10 Fast Blanking Input

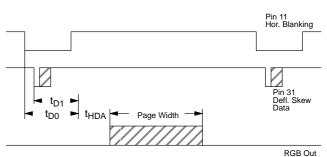

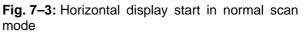

- 11 Horizontal Blanking Pulse Input/D2SYNC Input

- 12 Vertical Blanking Pulse Input

- 13 Reset Input

- 14 IM Bus Data Input/Output

- 15 IM Bus Ident Input

- 16 IM Bus Clock Input

- 17 A0 RAM Address Output

- 18 A1 RAM Address Output

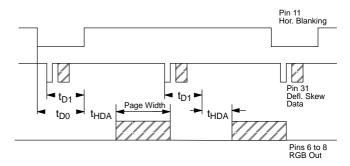

19 A2 RAM Address Output 20 N.C. 21 A3 RAM Address Output 22 A4 RAM Address Output 23 A5 RAM Address Output 24 A6 RAM Address Output 25 A7 RAM Address Output 26 A8 RAM Address Output 27 Data Input/Output 28 Read/Write Output 29 CAS Output 30 RAS Output 31 Skew Data Input 32 B Input 33 G Input 34 R Input 35 V<sub>SUP</sub> 37 N.C. 38 D2Data Input 39 V1 Video Input (LSB) 40 V2 Video Input

#### 3.2.2. 44-Pin PLCC Package

- 1 V2 Video Input

- 2 Leave Vacant

- 3 V3 Video Input

- 4 V4 Video Input

- 5 V5 Video Input

- 6 V6 Video Input (MSB)

- 7 GND

- 8 R Output

- 9 G Output

- 10 B Output

11 Fast Blanking Output 12 Fast Blanking Input 13 Horizontal Blanking Pulse Input / D2SYNC Input 14 Reset Input 15 IM Bus Data Input/Output 16 IM Bus Ident Input 17 IM Bus Clock Input 18 A0 RAM Address Output **19 Leave Vacant** 20 Leave Vacant 21 A1 RAM Address Output 22 A2 RAM Address Output 23 Vertical Blanking Pulse Input 24 A3 RAM Address Output 25 A4 RAM Address Output 26 A5 RAM Address Output 27 A6 RAM Address Output 28 A7 RAM Address Output 29 A8 RAM Address Output 30 Data Input/Output 31 Read/Write Output 32 CAS Output 33 RAS Output 34 Skew Data Input 35 B Input 36 G Input 37 R Input 38 GND **39 VSUP** 40 ΦM Main Clock Input 41 Leave Vacant 42 D2 Data Input 43 Leave Vacant

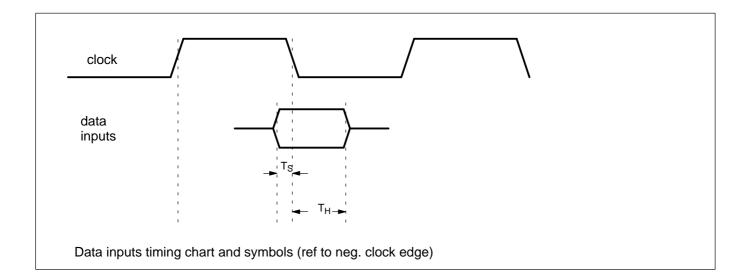

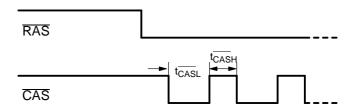

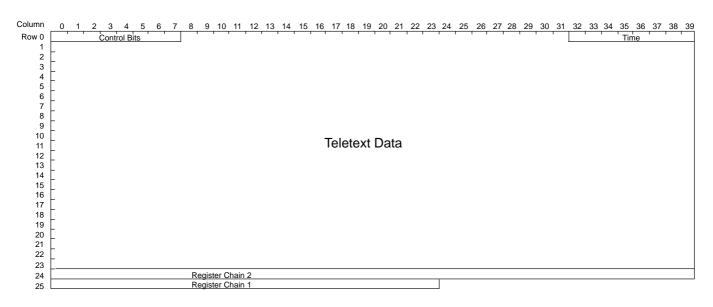

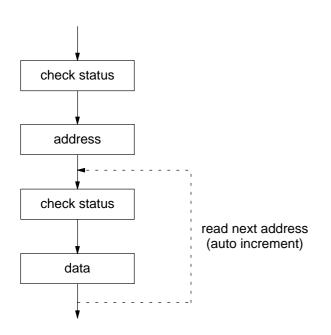

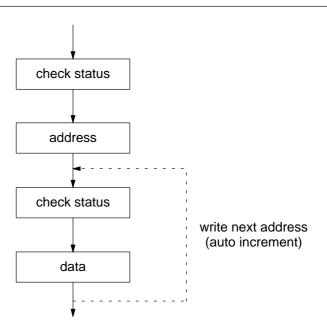

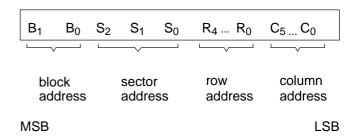

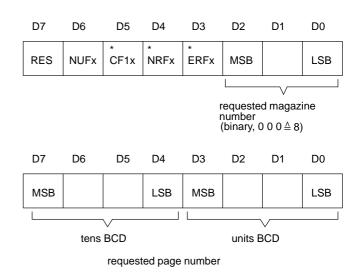

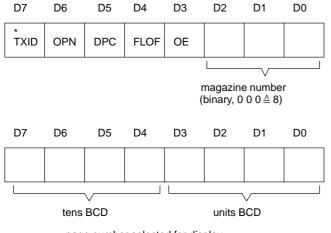

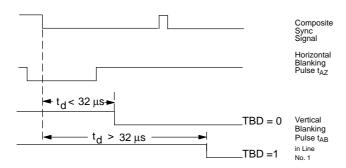

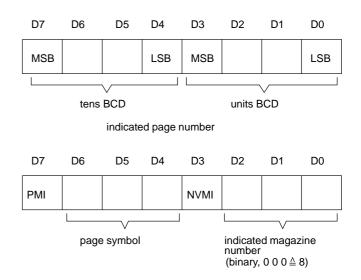

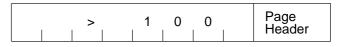

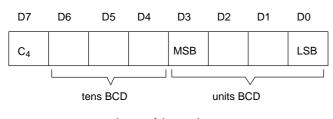

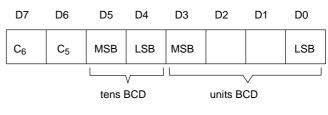

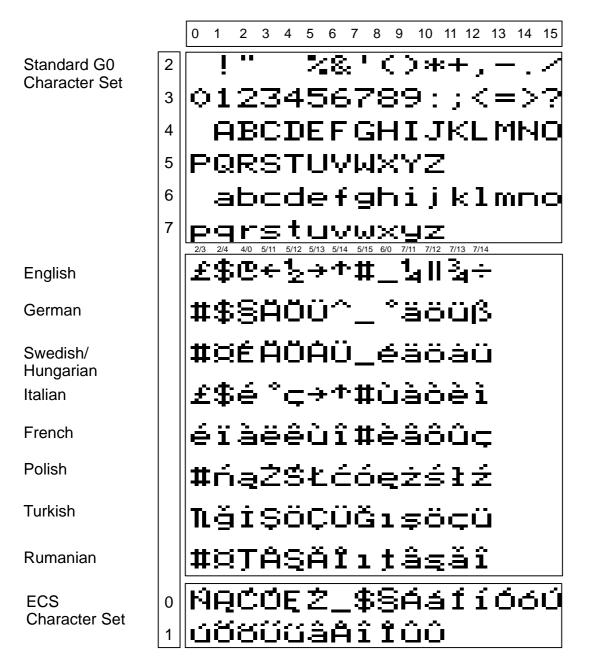

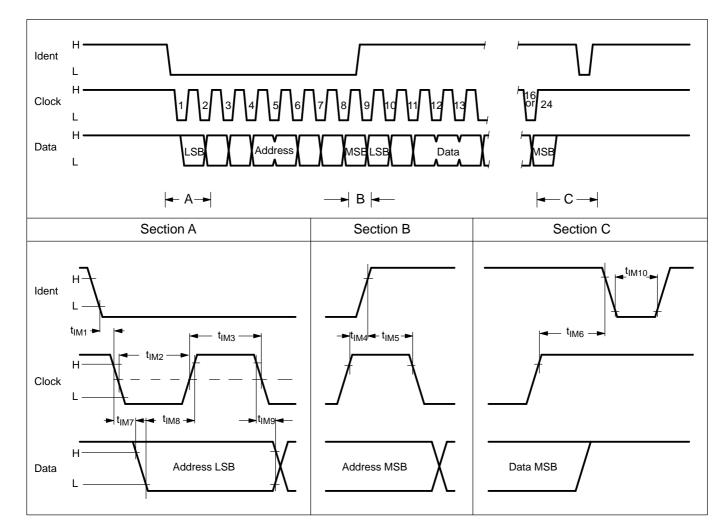

44 V1 Video Input (LSB)